# SS1102C Integrated MCU with Spread-Spectrum Transceiver (SST)

# **External Specification**

PRELIMINARY (V 1.8)

Siliconians, Inc. 4701 Patrick Henry Drive, Suite 501, Santa Clara, CA 95054 Tel: 408-748-8600 Fax: 408-748-8687 www.siliconians.com or info@siliconians.com

## **Table of Contents**

| 1. Description                                                                                                                                                                                                                                                                                                                                             | .1                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 2. Features                                                                                                                                                                                                                                                                                                                                                | ,1                                     |

| 3. SS1102C Block Diagram                                                                                                                                                                                                                                                                                                                                   | .2                                     |

| 4. Pin Description                                                                                                                                                                                                                                                                                                                                         | .3                                     |

| 5. CPU                                                                                                                                                                                                                                                                                                                                                     | .5                                     |

| <ul> <li>6. Memory organization</li> <li>6.1. Data memory</li> <li>6.2. Program memory</li> </ul>                                                                                                                                                                                                                                                          | .5                                     |

| <ul> <li>7. Special function registers</li> <li>7.1. Stack Pointer (SP)</li> <li>7.2. Data Pointer (DPTR)</li> <li>7.3. Program Status Word (PSW)</li> <li>7.4. Accumulator (ACC)</li> <li>7.5. B Register (B)</li> <li>7.6. Memory Size Register (MSIZ)</li> <li>7.7. Interrupts</li> </ul>                                                               | .8<br>.8<br>.9<br>.9                   |

| <ul> <li>8. Time Base Timer</li> <li>8.1. Overview</li> <li>8.2. Time Base Timer Control Register (TBCR)</li> <li>8.3. TB-Timer Counter Register (TBCNT)</li> <li>8.4. TB-Timer Data Register (TBDAT)</li> </ul>                                                                                                                                           | .10<br>.10<br>.11<br>.13               |

| <ul> <li>9. Capture Timers 1/2</li> <li>9.1. Overview</li> <li>9.2. Auto-Reload Mode</li> <li>9.3. Up Down-Count Mode</li> <li>9.4. Capture Mode</li> <li>9.5. Capture Timer Control Registers (CT1CR/CT2CR)</li> <li>9.6. Capture Timer-1 Status Registers (CT1SR)</li> <li>9.7. C-Timer Counter Registers</li> <li>9.8. C-Timer Data Register</li> </ul> | .15<br>.16<br>.16<br>.17<br>.18<br>.21 |

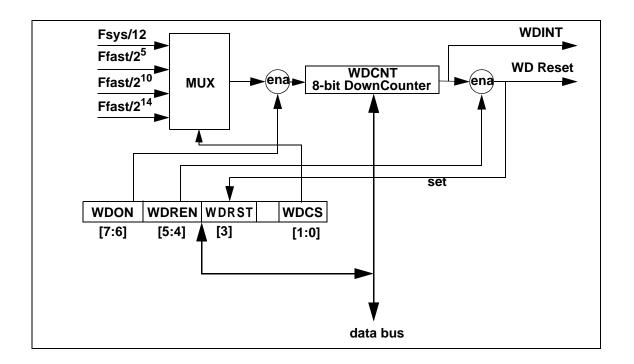

| <ul> <li>10. WatchDog Timer</li> <li>10.1. Overview</li> <li>10.2. WatchDog Timer Control Register (WDCR)</li> <li>10.3. WatchDog Timer Register (WDCNT)</li> <li>10.4. Operation</li> <li>11. SPI (Serial Peripheral Interface)</li> </ul>                                                                                                                | .25<br>.26<br>.28<br>.29               |

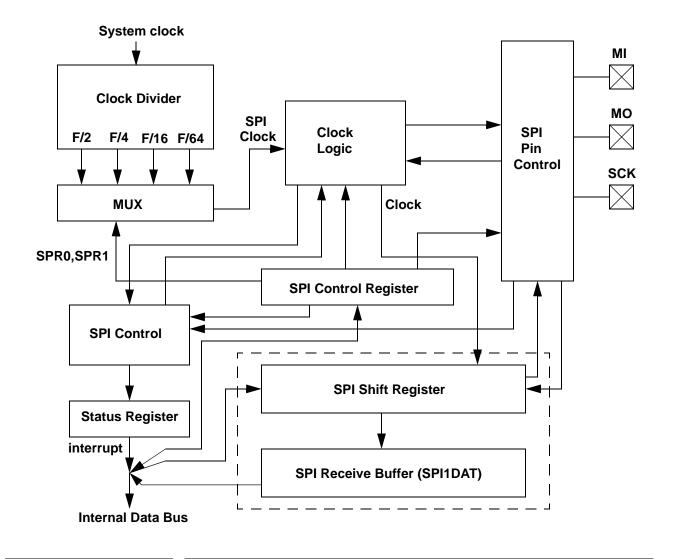

| 11. Str (Scharrenpierar Internace)                                                                                                                                                                                                                                                                                                                         |                                        |

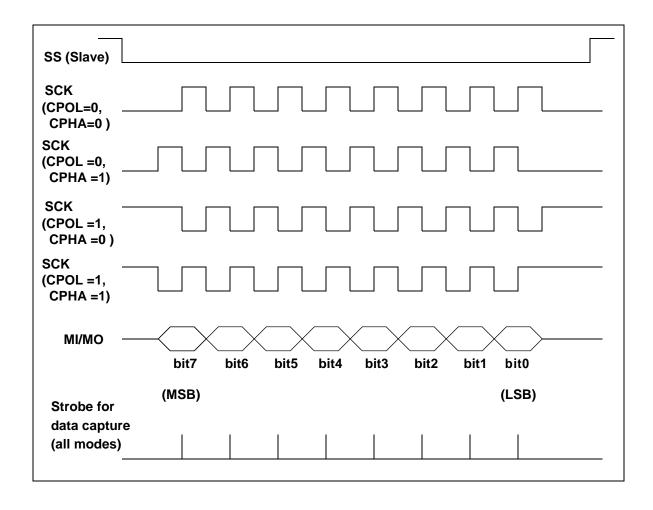

| 11.2. SPI Pin and Timing Description                      | 30 |

|-----------------------------------------------------------|----|

| 11.3. SPI Timing Description                              |    |

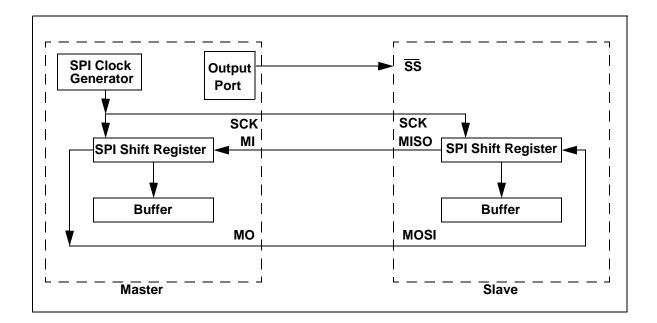

| 11.4. SPI Operation                                       |    |

| 11.5. SPI Control Register (SPICR)                        |    |

| 11.6. SPI Status Register (SPI1SR)                        |    |

| 11.7. SPI Shift Register (SPIDAT)                         |    |

| 12. Direct Sequence Spread Spectrum Baseband Modem (SSTM) | 37 |

| 12.1. Receiver                                            |    |

| 12.2. Transmitter                                         |    |

| 12.3. TDD Controller                                      |    |

| 12.4. FIFOs                                               |    |

| 12.5. Master Clock Generator                              |    |

| 12.6. Full-Duplex Operation                               |    |

| 12.7. TDD Protocol                                        |    |

| 12.8. System Delay                                        |    |

| 12.9. Timing Information                                  |    |

| 12.9.1 Full Duplex Operations                             |    |

| 12.9.2 Threshold Value Calculation                        | 43 |

| 12.10. Half-duplex Operation                              |    |

| 12.11. Reading the Signaling Word and S/N Data            |    |

| 12.12. Control Registers                                  |    |

| 12.13. SSTM Control Registers                             |    |

| 12.14. Configuration Information Bits                     |    |

| 12.15. RF/IF Analog Interface                             |    |

| 12.16. Programming the SSTM                               |    |

| 12.17. PN Sequence and UW Selection                       |    |

| 12.18. PN Sequence Selection                              |    |

| 12.19. UW Selection                                       |    |

| 12.20. Generating the PN and UW sequences                 | 57 |

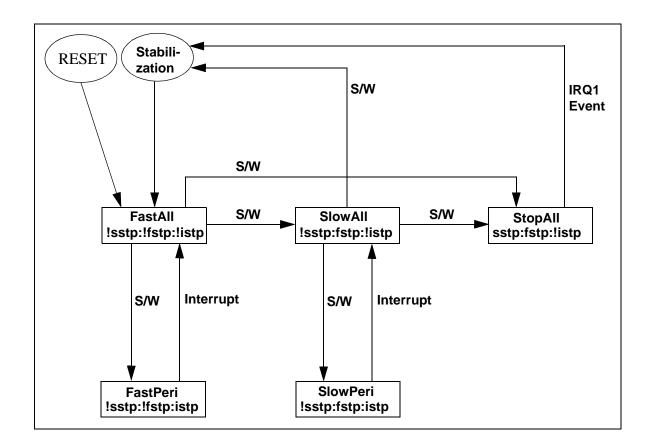

| 13. Power-Saving Modes                                    | 58 |

| 13.1. Overview                                            |    |

| 13.2. Mode Definition and Transition                      |    |

| 13.3. FastAll mode (a Clocking Mode)                      |    |

| 13.4. SlowAll mode (a Clocking Mode)                      | 60 |

| 13.5. StopAll mode (a Clocking Mode)                      | 60 |

| 13.6. FastPeri mode (a Clocking Mode)                     | 61 |

| 13.7. SlowPeri mode (a Clocking Mode)                     | 61 |

| 13.8. NorPin mode (a Pin State Mode)                      | 61 |

| 13.9. HIZ mode (a Pin State Mode)                         | 61 |

| 13.10. Power-Saving Control Register (PSCR)               |    |

| 13.11. Stop Release Register (SREL)                       |    |

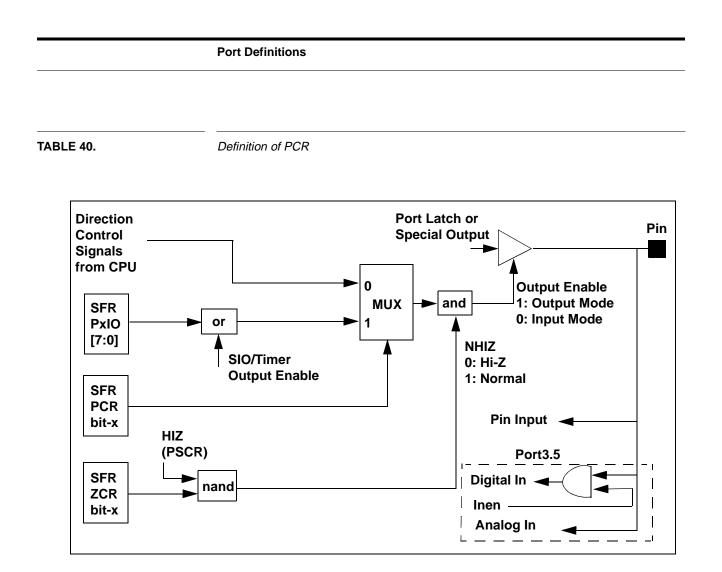

| 14. Port Definitions                                         | 65  |

|--------------------------------------------------------------|-----|

| 14.1. Overview                                               | 65  |

| 14.2. Read-Modify-Write Feature                              |     |

| 14.3. PCR (Port Control Register)                            | 67  |

| 14.4. ZCR (Hi-Z Control Register)                            | 68  |

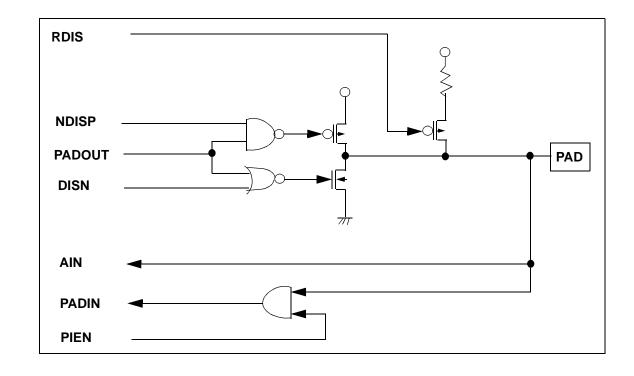

| 14.5. PAD Cell                                               |     |

| 14.6. P0 (Port-0)                                            | 69  |

| 14.7. P2 (Port-2)                                            | 73  |

| 14.8. P1 (Port-1)                                            |     |

| 14.9. P3 (Port-3)                                            |     |

| 14.10. Port-4                                                | 83  |

| 15. External Interrupts                                      | 87  |

| 15.1. Overview                                               | 87  |

| 15.2. Interrupt Control Block                                | 87  |

| 15.3. Interrupt Request Registers (INT0, INT1, INT2)         | 92  |

| 15.3.1 Interrupt Source Enable Registers (ISE0, ISE1, ISE2)  | 93  |

| 15.3.2 Interrupt Group Enable Register (IE)                  | 95  |

| 15.3.3 Interrupt Priority Register (IP)                      | 95  |

| 15.3.4 Interrupt Processing                                  | 96  |

| 16. SS1102C Special Modes                                    | 98  |

| 16.1. TEST ROM (Using Auxiliary RAM)                         |     |

| 16.2. EMULATION MODE                                         |     |

| 16.3. MULTICHIP PROGRAM MEMORY INTERFACE                     |     |

| 16.4. EXTERNAL MEMORY MODE                                   | 102 |

| 17. Comparator module                                        | 104 |

| 17.1. General Information                                    |     |

| 17.2. Functional Description                                 |     |

| 17.3. Block Diagram                                          |     |

| 17.4. Comparator Control Register                            |     |

| 17.5. Comparator I/O plot                                    |     |

| 18. Power-On Reset (POR)                                     |     |

| 18.1 General                                                 |     |

| 18.2. Operation                                              |     |

| 18.3. Crystal Oscillator Start-Up Time                       |     |

|                                                              |     |

| 19. Low Battery Detect (LBD) - Low Voltage Reset             |     |

| 19.1. General Information                                    |     |

| 19.2. Functional Description                                 |     |

| 19.3. Low Battery Detect, Low Voltage Reset Control Register |     |

|                                                              |     |

| 20. DC PARAMETRICS                                           | 114 |

| 20.1. I/O Characteristics                  |     |

|--------------------------------------------|-----|

| 21. AC Specifications                      |     |

| 21.1. TIMING WAVEFORMS                     | 115 |

| 22. Oscillator Pad Characteristics         | 116 |

| 23. SS1102C I/O PAD Information            | 117 |

| 23.1. I/O Type 1 and Type 3                | 117 |

| 23.2. I/O Type 2                           | 118 |

| 23.3. I/O Type 4: Input with static Pullup |     |

| 23.4. Oscillator-Pads with Enable-signal   |     |

| 24. PAD ASSIGNMENT TABLES                  |     |

| 25. Package                                |     |

| 26. Operating temperature:                 | 122 |

| 27. 100-pin Chip                           |     |

## 1. Description

The SS1102C is a CMOS integrated solution for direct sequence spread spectrum digital wireless data communication applications. The chip performs all CPU, baseband modem and peripheral control functions. A baseband spread spectrum modem, a microcontroller, and I/O interfaces are integrated into a single chip. The RF interface is suitable for most RF module designs. A low speed link data path allows for supervisory and setup functions, while the communication channel is used for full duplex data transmission.

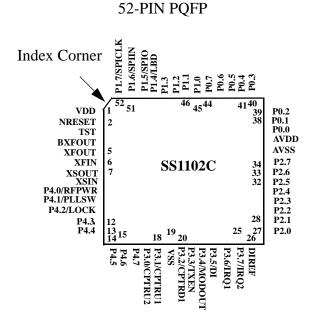

The chip can be delivered in the 52-pin or 100-pin package. The 100-pin version has an interface to the external EPROM. The 52-pin version is a mask version of the chip.

#### 2. Features

- Direct sequence spread spectrum transceiver

- Support for MSK

- RF interface signals

- Full and half duplex data transmission modes

- 125Kbps maximum data rate in half duplex mode

- 64Kbps maximum data rate in full duplex mode

- Low speed signalling full duplex data path

- 8051 compatible 8-bit CPU

- 16K bytes on-chip ROM

- 512 x 8 RAM

- Two capture timers

- WatchDog timer

- Time Base timer

- Programmable Serial Peripheral Interface (SPI)

- Low battery detect

- Programmable I/O lines

- Active, Low Power and Power Down Operation modes

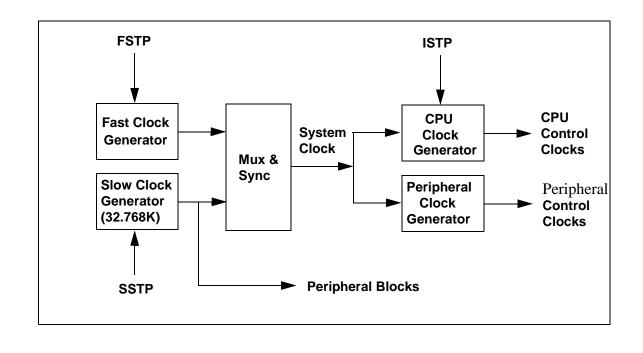

- Two on-chip oscillator circuits up to 24MHz Master clock and low speed 32KHz clock for the Low Power mode

- Power-on Reset

- Supply Voltage: 2.7V-5.5V

- 52-pin package

- Operating temperature: -20C to 85C

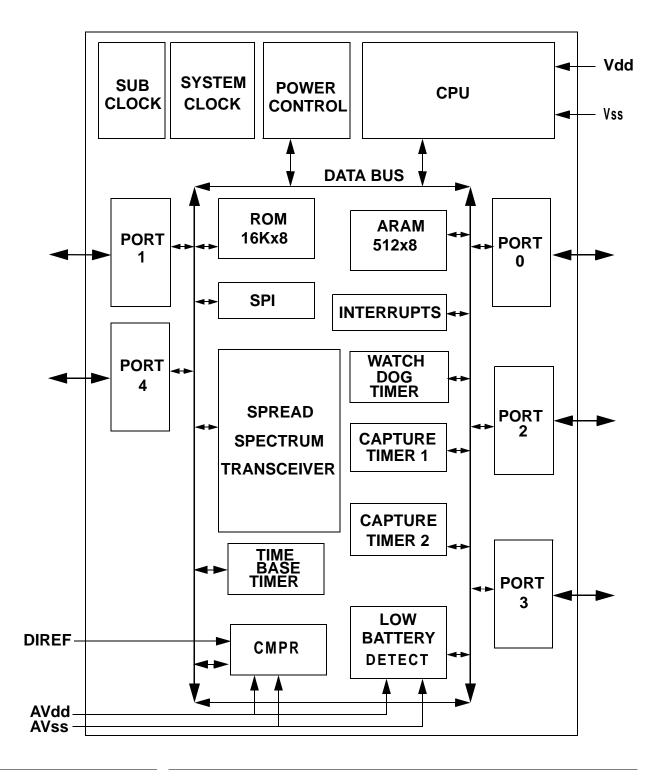

## 3. SS1102C Block Diagram

Figure 1.

SS1102C Block Diagram

## 4. Pin Description

| Port   | Pin # | Pin Name | I/О Туре   | Functions                                                  |

|--------|-------|----------|------------|------------------------------------------------------------|

| VDD    | 1     | Vdd      |            | Digital Supply Voltage                                     |

| NRESET | 2     | NRESET   |            | Reset                                                      |

| TST    | 3     | TST      |            | Test pin                                                   |

| BXFOUT | 4     | BXFOUT   |            | Buffered High Frequency Output                             |

| XFOUT  | 5     | XFOUT    | Oscillator | High frequency crystal output                              |

| XFIN   | 6     | XFIN     | Oscillator | High frequency crystal input                               |

| XSOUT  | 7     | XSOUT    | Oscillator | Slow frequency crystal output                              |

| XSIN   | 8     | XSIN     | Oscillator | Slow frequency crystal input                               |

| P4.0   | 9     | RFPWR    | I/O 3      | RF power switch output/ I/O                                |

| P4.1   | 10    | PLLSW    | I/O 3      | Phase-lock loop switch output/ I/O                         |

| P4.2   | 11    | LOCK     | I/O 3      | Lock Indicator                                             |

| P4.3   | 12    | I/O      | I/O 3      | Latched bi-directional I/O                                 |

| P4.4   | 13    | I/O      | I/O 3      | Latched bi-directional I/O                                 |

| P4.5   | 14    | I/O      | I/O 3      | Latched bi-directional I/O                                 |

| P4.6   | 15    | I/O      | I/O 3      | Latched bi-directional I/O                                 |

| P4.7   | 16    | I/O      | I/O 3      | Latched bi-directional I/O                                 |

| P3.0   | 17    | CPTRU2   | I/O 3      | Capture Timer 2                                            |

| P3.1   | 18    | CPTRU1   | I/O 3      | Capture Timer 1                                            |

| VSS    | 19    | Vss      |            | Digital Ground                                             |

| P3.2   | 20    | CPTRD1   | I/O 3      | Capture Timer 1/Down Counter                               |

| P3.3   | 21    | TXEN     | I/O 3      | Transmitter enable output/ I/O                             |

| P3.4   | 22    | MODOUT   | I/O 3      | Modulated output (chips output)                            |

| P3.5   | 23    | DI       | I/O 2      | Digital (DI) / Analog (DI1) Data<br>Input                  |

| P3.6   | 24    | IRQ1     | I/O 3      | External Interrupt 0                                       |

| P3.7   | 25    | IRQ2     | I/O 3      | External Interrupt 1                                       |

| DIREF  | 26    | DIREF    | I/O 3      | Analog Data Input Comparator<br>External reference voltage |

| Port | Pin # | Pin Name | I/О Туре | Functions                  |

|------|-------|----------|----------|----------------------------|

| P2.0 | 27    | I/O      | I/O 2    | Latched bi-directional I/O |

| P2.1 | 28    | I/O      | I/O 2    | Latched bi-directional I/O |

| P2.2 | 29    | I/O      | I/O 2    | Latched bi-directional I/O |

| P2.3 | 30    | I/O      | I/O 2    | Latched bi-directional I/O |

| P2.4 | 31    | I/O      | I/O 2    | Latched bi-directional I/O |

| P2.5 | 32    | I/O      | I/O 2    | Latched bi-directional I/O |

| P2.6 | 33    | I/O      | I/O 2    | Latched bi-directional I/O |

| P2.7 | 34    | I/O      | I/O 2    | Latched bi-directional I/O |

| AVSS | 35    | AVss     |          | Analog Ground              |

| AVDD | 36    | AVdd     |          | Analog Supply Voltage      |

| P0.0 | 37    | I/O      | I/O 2    | Latched bi-directional I/O |

| P0.1 | 38    | I/O      | I/O 2    | Latched bi-directional I/O |

| P0.2 | 39    | I/O      | I/O 2    | Latched bi-directional I/O |

| P0.3 | 40    | I/O      | I/O 2    | Latched bi-directional I/O |

| P0.4 | 41    | I/O      | I/O 2    | Latched bi-directional I/O |

| P0.5 | 42    | I/O      | I/O 2    | Latched bi-directional I/O |

| P0.6 | 43    | I/O      | I/O 2    | Latched bi-directional I/O |

| P0.7 | 44    | I/O      | I/O 2    | Latched bi-directional I/O |

| P1.0 | 45    | I/O      | I/O 2    | Latched bi-directional I/O |

| P1.1 | 46    | I/O      | I/O 2    | Latched bi-directional I/O |

| P1.2 | 47    | I/O      | I/O 2    | Latched bi-directional I/O |

| P1.3 | 48    | I/O      | I/O 2    | Latched bi-directional I/O |

| P1.4 | 49    | LBD      | I/O 2    | Low battery detect         |

| P1.5 | 50    | SPIO     | I/O 2    | Serial Out                 |

| P1.6 | 51    | SPIIN    | I/O 2    | Serial In                  |

| P1.7 | 52    | SPICLK   | I/O 2    | Serial Clock               |

## TABLE 1.

Pin Description

CPU

Figure 2.

SS1102C Pinout

#### 5. CPU

- High performance CMOS 8-bit CPU with the industry standard 80C51 instruction set.

- Extensive boolean processing (single bit logic) capabilities

- Arithmetic: 8 bit including multiply and divide

- Jumps, 8/16 bit address, conditional and unconditional

- Logical separation of program and data memory

- Six addressing modes

- Maximum operating speed 24MHz.

### 6. Memory organization

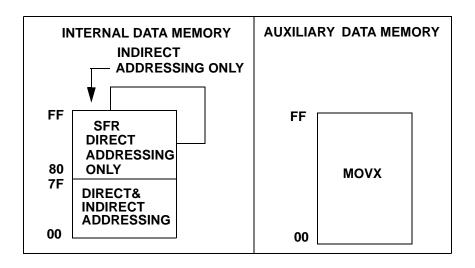

#### 6.1. Data memory

The SS1102C has separate address space for Program Memory and Data Memory.

The SS1102C has 512 bytes of onchip data space, 256 bytes must be accessed by MOVX.

By direct and indirect addressing the lowest 128 bytes can be accessed. Then the next 128 bytes are accessed by indirect addressing while direct addressing in this area will access the SFR registers. With the MOVX command there are up to 256 bytes of data memory accessible. DPH should be "0" to use Port.0 and Port2 as GPIO ports.

Figure 3.

The SS1102C Data Memory

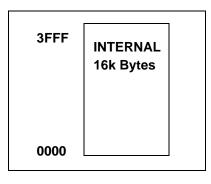

#### 6.2. Program memory

The SS1102C program memory will fetch 16Kbytes from internal mask ROM.

Figure 4.

The SS1102C Program Memory

## 7. Special function registers

The SS1102C special function registers (SFR) are accessed with direct memory addressing in the memory space from 80H to FFH. The table below shows the location of each register. The description of the register functions are in the respective peripheral block descriptions and the architectural overview section.

| Lo \ Hi | 8                | 9                | Α                          | В                | С                | D                | Е                | F              |

|---------|------------------|------------------|----------------------------|------------------|------------------|------------------|------------------|----------------|

| 0       | P0               | P1               | P2                         | P3               | P4               | PSW              | ACC              | В              |

| 1       | SP               |                  | WDCR                       | TBCR             | SSTMCR           | CT1CR            | CT2CR            | SPI1CR         |

| 2       | DPL              |                  | WDCNT                      | TBCNT            |                  | CT1CNTL          | CT2CNTL          | SPI1DAT        |

| 3       | DPH              |                  |                            | TBDAT            |                  | CT1CNTH          | CT2CNTH          | SPI1SR         |

| 4       | LBDCR            |                  |                            |                  |                  | CT1DATL          | CT2DATL          |                |

| 5       | CMPRCR           |                  |                            |                  |                  | CT1DATH          | CT2DATH          |                |

| 6       |                  | SREL             | XICR0                      |                  |                  | CT1SR            |                  |                |

| 7       |                  | PSCR             |                            |                  |                  | ISE0             | ISE1             | ISE2           |

| 8       |                  |                  | IE                         | IP               | 0:IEIS<br>1:UW2  | INT0             | INT1             | INT2           |

| 9       |                  |                  | PONOP                      | P1NOP            | P2NOP            | P3NOP            | P4NOP            |                |

| Α       |                  | PCR              | P0IO                       | P1IO             | P2IO             | P3IO             | P4IO             |                |

| В       |                  | ZCR              | PORD                       | P1RD             | P2RD             | P3RD             | P4RD             |                |

| С       |                  |                  |                            |                  |                  |                  |                  |                |

| D       |                  |                  |                            |                  |                  |                  |                  |                |

| E       | 0: CIL<br>1: CIL | 0:LCK<br>1:TXSHH | 0:TXSW/<br>RXSW<br>1:RXSHH | 0:PNA0<br>1:PNC0 | 0:PNA1<br>1:PNC1 | 0:PNA2<br>1:PNC2 | 0:PNA3<br>1:PNC3 | 0:RDI<br>1:UW1 |

| F       | 0: CIH<br>1: UW0 | 0: -<br>1:TXSHL  | 0:SN<br>1:RXSHL            | 0:PNB0<br>1:PND0 | 0:PNB1<br>1:PND1 | 0:PNB2<br>1:PND2 | 0:PNB3<br>1:PND3 | MSIZ           |

TABLE 2.

Special Function Registers Description

The SFR register definitions are described within each peripheral block description and the general CPU registers SP, DPTR, PSW, ACC, B, and MSIZ are described below. The underlined names are the registers for the CPU and the dashed lines are for registers used in standard 8051 devices but not used by the SS1102C microcontroller.

#### 7.1. Stack Pointer (SP)

The SP register contains the stack pointer. The stack pointer is used to load the program counter into memory during LCALL and ACALL instructions, and is used to retrieve the program counter from memory in RET and RETI instructions. The stack may also be saved or loaded using PUSH and POP instructions, which also increment and decrement the stack pointer. The stack pointer points to the top location of the stack. On reset the stack pointer is set to 07 hex.

#### 7.2. Data Pointer (DPTR)

The Data Pointer (DPTR) is 16 bits in size, and consists of two registers, the Data Pointer High byte (DPH), and the Data Pointer Low byte (DPL). Two 16 bit operations are possible on this register, they are load immediate and increment. This register is used for 16 bit address external memory accesses, for offset code byte fetches, and for offset program jumps. On reset the value of this register is 0000 hex.

#### 7.3. Program Status Word (PSW)

This register contains status information resulting from CPU and ALU operation. The bit definitions are given below:

- **PSW.7** CY. ALU carry flag.

- PSW.6 AC. ALU auxiliary carry flag.

- **PSW.5** F0. General purpose user definable flag.

- **PSW.4** RS1. Register bank select bit 1.

- **PSW.3** RS0. Register bank select bit 0.

- **PSW.2** OV. ALU overflow flag.

- **PSW.1** F1. User definable flag.

- **PSW.0** P. Parity flag. Set each instruction cycle to indicate odd/even parity in the accumulator.

On reset this register returns 00 hex.

The register bank select bits operate as follows

| RS1 | RS0 | Register Bank Select             |

|-----|-----|----------------------------------|

| 0   | 0   | RB0. Registers from 00 - 07 hex. |

| 0   | 1   | RB1. Registers from 08 - 0F hex. |

| 1   | 0   | RB2. Registers from 10 - 17 hex. |

| 1   | 1   | RB3. Registers from 18 - 1F hex. |

#### TABLE 3.

Register bank select bits

#### 7.4. Accumulator (ACC)

This register provides one of the operands for most ALU operations. In the instruction table it is denoted as "A".

On reset this register returns 00 hex.

#### 7.5. B Register (B)

This register provides the second operand for multiply or divide instructions. Otherwise it may be used as a scratch pad register.

On reset this register returns 00 hex.

#### 7.6. Memory Size Register (MSIZ)

The purpose of this register is to define the amount of available internal program memory. The amount available is:

$(MSIZ + 1) \times 256.$

On reset this register returns 3F hex or 16K of internal program memory.

- 16K byte internal ROM

- A total of 512 bytes of on-chip data RAM:

- 256 bytes standard RAM

- 256 bytes of additional on-chip data memory accessible by the MOVX command (XRAM).

#### 7.7. Interrupts

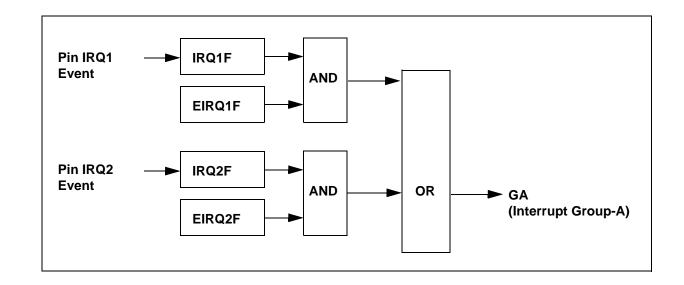

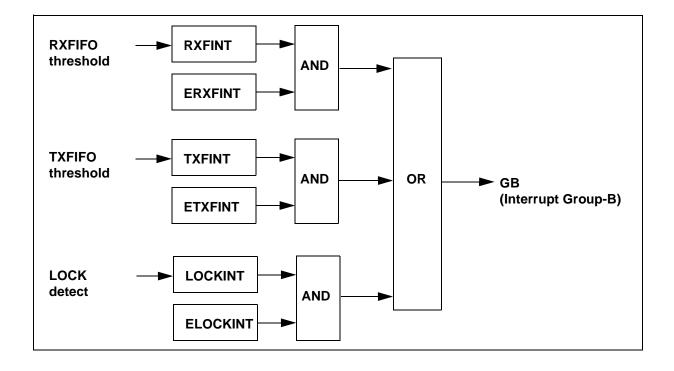

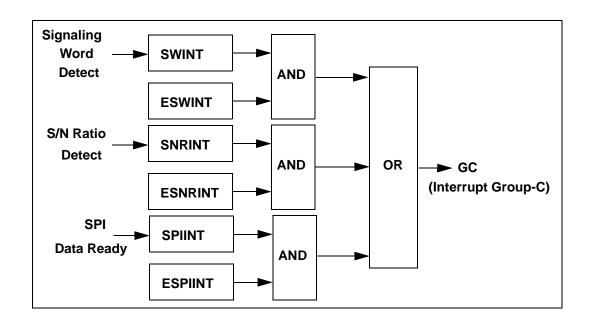

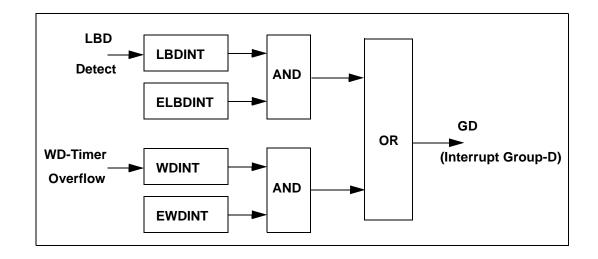

- Two external interrupt input pins (IRQ1, IRQ2)

- Eleven internal interrupt sources. The following peripheral blocks can generate interrupt request: Watchdog Timer, Time Base Timer, Capture Timer 1, Capture Timer 2, SPI, TXFIFO, RXFIFO, Signaling Word, Signal/Noise Ratio, and Lock, LBD

#### 8. Time Base Timer

#### 8.1. Overview

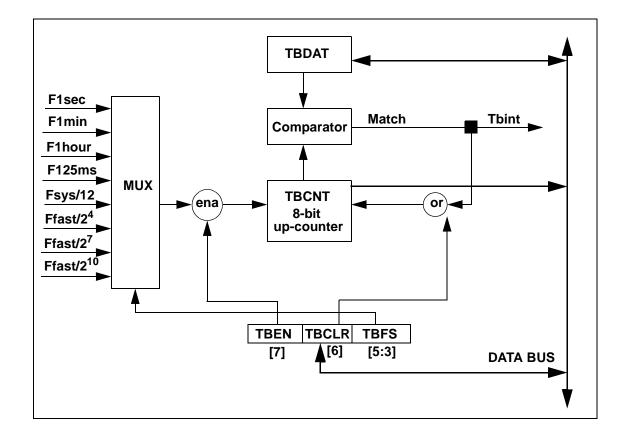

The Time Base Timer (TB-Timer) is an 8-bit auto-reload timer. The TB-Timer is composed of a input frequency select MUX, an 8-bit up-counter(TBCNT), a Comparator, an 8-bit data register(TBDAT), and a control register(TBCR).

The TB-Timer has the 8 counting clocks that can be selected by TBFS[5:3]. Four of the clocks come from the System Clock block, i.e.  $F_{1SEC}$ ,  $F_{1MIN}$ ,  $F_{1HOUR}$ , and  $F_{125mS}$ . If the slow oscillator is stopped, these four clocks will stop too. These four clocks will be very useful to generate a real time interval and to minimize the number of CPU wake-ups. The period of the  $F_{sys}/12$  clock is one machine cycle or one fastest instruction cycle. This clock will run during any power-saving mode except the StopAll mode. During the FastAll or FastPeri mode, the  $F_{sys}/12$  clock is equal to  $F_{fast}/12$ . During the SlowAll or SlowPeri mode, the  $F_{sys}/12$  clock is equal to  $F_{slow}/12$ . The  $F_{fast}/2^4$ ,  $F_{fast}/2^7$ , and  $F_{fast}/2^{10}$  can be used during the FastAll or FastPeri mode only.

After the TBEN bit is set to high, the TBCNT will start to count the negative edge of an input clock. When the TBEN bit is low, the Match signal is never generated even though the contents of the TBDAT and TBCNT are the same. The TBCNT is the 8-bit up-counter that can be cleared by the TBCLR bit or the Match signal. The TBCNT is a modulo-N counter (from 0 to N-1), N is the content of the TBDAT. The match signal will always set the TBINT bit to high. The TBINT bit can be cleared by the TB-Timer Interrupt Acknowledge or by software.

#### Figure 5.

Time Base Timer

## 8.2. Time Base Timer Control Register (TBCR)

| Address        | B1H                | B1H                    |                                                   |                                                   |                                                   |                       |                         |          |  |

|----------------|--------------------|------------------------|---------------------------------------------------|---------------------------------------------------|---------------------------------------------------|-----------------------|-------------------------|----------|--|

| Bit Addr.      |                    |                        |                                                   |                                                   |                                                   |                       |                         |          |  |

| BIT            | 7                  | 6                      | 5                                                 | 4                                                 | 3                                                 | 2                     | 1                       | 0        |  |

| NAME           | TBEN               | TBCLR                  | TBFS2                                             | TBFS1                                             | TBFS0                                             | HTST                  | MTST                    |          |  |

| Definition     | TB timer<br>ENable | TB<br>counter<br>CLeaR | TB timer<br>input<br>Frequency<br>Select<br>bit-2 | TB timer<br>input<br>Frequency<br>Select<br>bit-1 | TB timer<br>input<br>Frequency<br>Select<br>bit-0 | Hour<br>Clock<br>Test | Minute<br>Clock<br>Test | Reserved |  |

| Reset<br>Value | 0                  | 0                      | 0                                                 | 0                                                 | 0                                                 | 0                     | 0                       | 0        |  |

#### Time Base Timer

| Read/<br>Write by<br>Software | R/W | R/W<br>Always 0<br>read. | R/W | R/W | R/W | R/W | R/W | R |

|-------------------------------|-----|--------------------------|-----|-----|-----|-----|-----|---|

| Write by<br>Hardware          |     |                          |     |     |     |     |     |   |

TABLE 4.

Definition of TBCR

| Name      | Bit    | Description                                                                                                                                                                                                                                                                                                                                   |

|-----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TBEN      | 7      | TB timer ENable bit<br>[Bit Status: 0 (Initial Value)]<br>A selected input clock is halted. The TBCNT keeps the counter value.<br>[Bit Status: 1]<br>A selected input clock runs. The TBCNT counts up the negative edge of the selected clock.                                                                                                |

| TBCLR     | 6      | TB counter CLeaR bit<br>If this bit is written with high, the TBCNT (8-bit up-counter) of the TB Timer will be cleared to<br>00H. Writing low will not affect anything. When read, a low(0) will be always read.                                                                                                                              |

| TBFS[5:3] | 5 to 3 | TB timer input clock Frequency Select bits<br>[Bit Status: 000 (Initial Value)] $F_{1SEC}$<br>[Bit Status: 001] $F_{1MIN}$<br>[Bit Status: 010] $F_{1HOUR}$<br>[Bit Status: 011] $F_{125mS}$<br>[Bit Status: 100] $F_{sys}/12$<br>[Bit Status: 101] $F_{fast}/2^4$<br>[Bit Status: 110] $F_{fast}/2^7$<br>[Bit Status: 111] $F_{fast}/2^{10}$ |

| HTST      | 2      | Hour clock Test bit<br>[Bit Status: 0 (Initial Value)]<br>Normal hour clock signal is used for F <sub>1hour</sub> .<br>[Bit Status: 1]<br>A test mode using XSout (32.768KHz) for F <sub>1hour</sub> .<br>Note: The bit can only be set either under FastAll or FastPeri modes.<br>User should write a 0 to this bit.                         |

| MTST      | 1      | Minute clock Test bit<br>[Bit Status: 0 (Initial Value)]<br>Normal minute clock signal is used for F <sub>1min</sub> .<br>[Bit Status: 1]<br>A test mode using the XSout (32.768KHz) for F <sub>1min</sub> .<br>Note: The bit can only be set either under FastAll or FastPeri modes.<br>User should write a 0 to this bit.                   |

| TBINT     | 0      | Reserved bits                                                                                                                                                                                                                                                                                                                                 |

TABLE 5.

Description of TBCR

## 8.3. TB-Timer Counter Register (TBCNT)

| Address                       | B2H                                                                                                 |                                                                      |                                                                      |                                                                      |                                                                      |                                                                      |                                                                      |                                                                      |  |

|-------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|--|

| Bit Addr.                     | None                                                                                                |                                                                      |                                                                      |                                                                      |                                                                      |                                                                      |                                                                      |                                                                      |  |

| BIT                           | 7                                                                                                   | 6                                                                    | 5                                                                    | 4                                                                    | 3                                                                    | 2                                                                    | 1                                                                    | 0                                                                    |  |

| NAME                          | TBCNT[7:0                                                                                           | ]                                                                    |                                                                      |                                                                      |                                                                      |                                                                      |                                                                      |                                                                      |  |

| Definition                    | TB-timer CouNTer register bit 7 to 0<br>(Modulo N Up-counter: 00 to N-1, N is the content of TBDAT) |                                                                      |                                                                      |                                                                      |                                                                      |                                                                      |                                                                      |                                                                      |  |

| Reset<br>Value                | 0                                                                                                   | 0                                                                    | 0                                                                    | 0                                                                    | 0                                                                    | 0                                                                    | 0                                                                    | 0                                                                    |  |

| Read/<br>Write by<br>Software | R                                                                                                   | R                                                                    | R                                                                    | R                                                                    | R                                                                    | R                                                                    | R                                                                    | R                                                                    |  |

| Write by<br>Hardware          | Written<br>with a new<br>count<br>value<br>0 or 1.<br>0 by<br>TBCLR.                                | Written<br>with a new<br>count<br>value<br>0 or 1.<br>0 by<br>TBCLR. | Written<br>with a new<br>count<br>value<br>0 or 1.<br>0 by<br>TBCLR. | Written<br>with a new<br>count<br>value<br>0 or 1.<br>0 by<br>TBCLR. | Written<br>with a new<br>count<br>value<br>0 or 1.<br>0 by<br>TBCLR. | Written<br>with a new<br>count<br>value<br>0 or 1.<br>0 by<br>TBCLR. | Written<br>with a new<br>count<br>value<br>0 or 1.<br>0 by<br>TBCLR. | Written<br>with a new<br>count<br>value<br>0 or 1.<br>0 by<br>TBCLR. |  |

#### TABLE 6.

Definition of TBCNT

| Name       | Bit    | Description                                                                                                                                                                                                                                                                                                                                                                                           |

|------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TBCNT[7:0] | 7 to 0 | TB-timer CouNTer bits<br>A Modulo-N (00 to N-1) up-counter. N is the content of TBDAT.<br>This counter counts up from 00H to N-1. Then, the counter will go back to 00H and the com-<br>parator will generate a match signal. The counter will not stop after the Match. Thus, the TB-<br>Timer will generate continuous Match signals with a fixed period. The TB-Timer is an auto-<br>reload timer. |

#### TABLE 7.

Description of TBCNT

| Address                       | B3H         |                                  |      |      |      |      |      |      |

|-------------------------------|-------------|----------------------------------|------|------|------|------|------|------|

| Bit Addr.                     | None        |                                  |      |      |      |      |      |      |

| BIT                           | 7           | 6                                | 5    | 4    | 3    | 2    | 1    | 0    |

| NAME                          | TBDAT[7:0]  |                                  |      |      |      |      |      |      |

| Definition                    | TB-timer D/ | B-timer DATa register bit 7 to 0 |      |      |      |      |      |      |

| Reset<br>Value                | 0           | 0                                | 0    | 0    | 0    | 0    | 0    | 0    |

| Read/<br>Write by<br>Software | R/W         | R/W                              | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| Write by<br>Hardware          | none        | none                             | none | none | none | none | none | none |

## 8.4. TB-Timer Data Register (TBDAT)

TABLE 8.

Definition of TBDAT

| Name       | Bit    | Description                                                                                                                                                            |

|------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TBDAT[7:0] | 7 to 0 | TB-timer DATa bits                                                                                                                                                     |

|            |        | [The first Match period]                                                                                                                                               |

|            |        | TB-Timer Match signal period = (1 / F <sub>selected-clock</sub> ) X (TBDAT + 1)                                                                                        |

|            |        | - Deviation period                                                                                                                                                     |

|            |        | 0 <= Deviation period < (1 / F <sub>selected-clock</sub> )                                                                                                             |

|            |        | If any clock, which are divided from XSout(32.768KHz), is selected, the Deviation period can be minimized because the Slow Clock prescaler can be cleared by software. |

|            |        | [The second or later Match period]                                                                                                                                     |

|            |        | TB-Timer Match signal period = (1 / F <sub>selected-clock</sub> ) X TBDAT<br>(No Deviation period)                                                                     |

TABLE 9.

Description of TBDAT

## 9. Capture Timers 1/2

#### 9.1. Overview

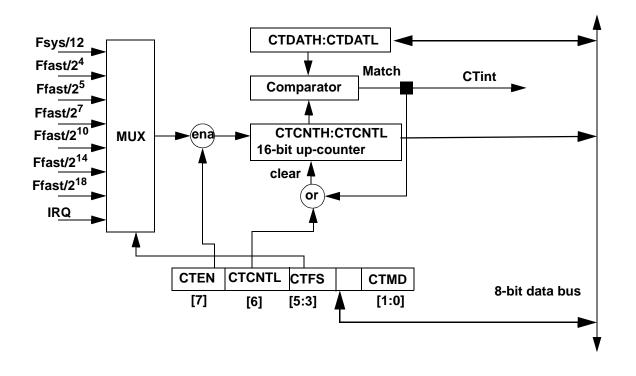

There are two 16-bit Capture Timer in the MCU, C-Timer1 and C-Timer2. Capture-Timer1 (or C-Timer1) can be used as an Auto-Reload Timer, an Event Counter, an Up Down-Counter or a Capture Timer. Capture-Timer2 (or C-Timer2) can be used as an Auto-Reload Timer, an Event Counter or a Capture Timer. A C-Timer is composed of a input frequency select MUX, a 16-bit up down-counter(16-bit up-counter for C-Timer2), a Comparator, a 16-bit data register(CT1DATH-CT1DATL, CT2DATH-CT2DATL), an Edge Detector for Capture, and a control register(CT1CR, CT2CR).

C-Timer1 can operate in three different modes. They are Auto-Reload Mode, Up Down-Count Mode and Capture Mode. All of these modes can be selected by the CT1MD[2:0] bits in the CT1CR. On the other hand, C-Timer2 can only operate in two different modes. They are Auto-Reload Mode and Capture Mode. All of these modes can be selected by the CT2MD[1:0] bits in the CT2CR.

In Auto-Reload Mode, the C-Timer can be used as an Auto-Reload Timer and an Auto-Reload Event Counter. In Up Down-Count Mode, C-Timer1 can be used as an Up Down-Counter. In Capture mode, the C-Timer can be used as a Capture Timer.

Figure 6.

Capture Timer in Auto-Reload Mode

#### 9.2. Auto-Reload Mode

If the CT1MD[2:0] bits in the CT1CR are 000, the C-Timer1 will operate in the Auto-Reload Mode.

If the CT2MD[1:0] bits in the CT2CR are 00, the C-Timer2 will operate in the Auto-Reload Mode.

A C-Timer has 8 counting clocks that can be selected by CT1FS[2:0] (or CT2FS[2:0]). The period of the  $F_{sys}/12$  clock is one machine cycle or one fastest instruction cycle. This clock will be run during any power-saving mode except the StopAll mode. During the FastAll or FastPeri mode, the  $F_{sys}/12$  clock is equal to  $F_{fast}/12$ . During the SlowAll or SlowPeri mode, the  $F_{sys}/12$  clock is equal to  $F_{slow}/12$ . The  $F_{fast}/2^4$ ,  $F_{fast}/2^5$ ,  $F_{fast}/2^7$ ,  $F_{fast}/2^{10}$ ,  $F_{fast}/2^{14}$ , and  $F_{fast}/2^{18}$  can be used during the FastAll or FastPeri mode only. Two external interrupt pins(CPTRU1 and CPTRU2) are connected to the C-Timer1 and 2. Thus, the timers can be used as the Event Counters. To use this timer as an Event Counter, the CPTRU1 (or CPTRU2) should be assigned as an input port by the port control register.

After the CT1EN(or CT2EN) bit is set to high, the CT1CNTH & CT1CNTL (or CT2CNTH & CT2CNTL) will start to count up the negative edge of a selected input clock. When the CT1EN (or CT2EN) bit is low, the Match signal is never generated even though the contents of the CT1DATH & CT1DATL (or CT2DATH & CT2DATL) and CT1CNTH & CT1CNTL (or CT2CNTH & CT2CNTL) are the same. In Auto-Reload Mode, CT1CNTH & CT1CNTL (or CT2CNTH & CT2CNTL) act as a 16-bit up-counter that can be cleared by the CT1CNTLR (or CT2CNTH & CT2CNTL) is a modulo-N counter (from 0 to N-1), N is the content of the CT1DATH & CT1DATL (or CT2DATH & CT2DATL) is a modulo-N counter (from 0 to N-1). The match signal will always set the CT1INT (or CT2INT) bit to high. The CT1INT (or CT2INT) bit can be cleared by a C-Timer Interrupt Acknowledge or software.

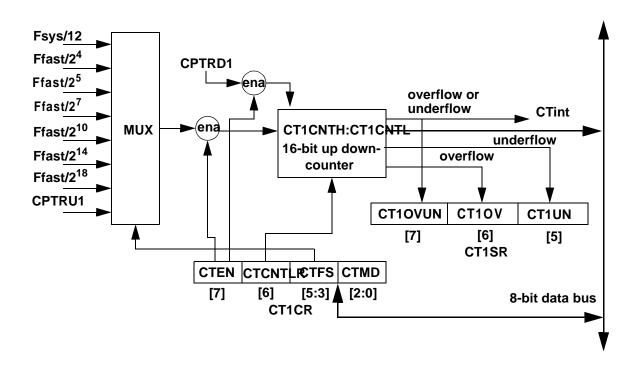

#### 9.3. Up Down-Count Mode

If the CT1MD[2:0] bits in the CT1CR are 1XX (X means don't care), the C-Timer1 will operate in the Up Down-Count Mode.

After the CT1EN bit is set to high, the 16-bit up down-counter(CT1CNTH & CT1CNTL) will start to count. It counts up on the negative edge of CPTRU1 and counts down on the negative edge of CPTRD1. To use CPTRU1, CT1FS[5:3] must set to 111. In Up Down-Count Mode, CT1CNTH & CT1CNTL act as a 16-bit up down-counter that can be cleared by the CT1CNTLR bit. The CT1CNTH & CT1CNTL is a modulo-65536 counter (from 0 to 65535). The overflow signal will set the CT1OV bit in CT1SR to high and the underflow signal will set the CT1UN bit in CT1SR to high. Both the overflow and underflow signal will always set the CT1INT bit in INT2 register and CT1OVUN bit in CT1SR to high. The CT1INT bit can be cleared by a C-Timer Interrupt Acknowledge or software, and CT1OV, CT1UN and CT1OVUN can be cleared by reading the CT1SR. Another Capture-Timer1 interrupt will not be generated if CT1OVUN is still not being cleared.

Figure 7.

Capture Timer 1 in Up-Down Count Mode

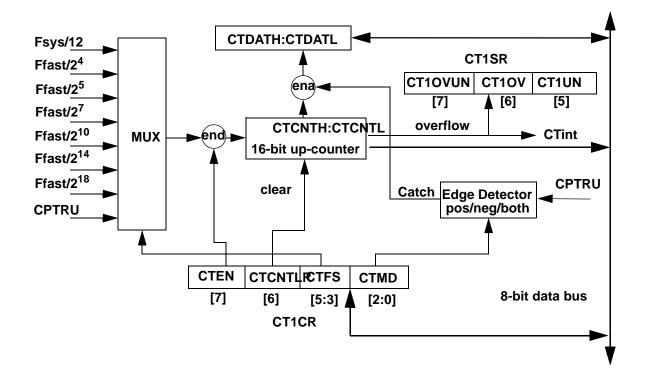

#### 9.4. Capture Mode

If the CT1MD[2:0] bits in the CT1CR are 001, 010, or 011, the C-Timer1 will operate in the Capture Mode. Counting clock selection feature is the same with the Auto-Reload Mode.

If the CT2MD[1:0] bits in the CT2CR are 01, 10, or 11, the C-Timer2 will operate in the Capture Mode. Counting clock selection feature is the same with the Auto-Reload Mode.

After the CT1EN (or CT2EN) bit is set to high, the 16-bit counter (CT1CNTH & CT1CNTL or CT2CNTH & CT2CNTL) will start to count up the negative edge of a selected input clock. In Capture Mode, CT1CNTH & CT1CNTL (or CT2CNTH & CT2CNTL) act as a 16-bit up-counter that can be cleared by the CT1CNTLR (or CT2CNTLR) bit. The CT1CNTH & CT1CNTL (or CT2CNTH & CT2CNTL) is a modulo-65536 counter (from 0 to 65535). The overflow signal will always set the CT1INT (or CT2INT) bit and CT1OVUN bit in CT1SR to high. The overflow signal also set the CT1OV to high. The CT1INT (or CT2INT) bit can be cleared by a C-Timer Interrupt Acknowledge or software, and CT1OV and CT1OVUN can be cleared by reading the CT1SR. Another Capture-Timer1 interrupt will not be generated if CT1OVUN is still not being cleared.

During up-counting, the content of 16-bit counter (CT1CNTH & CT1CNTL or CT2CNTH & CT2CNTL) will be capture into the 16-bit latch (CT1DATH & CT1DATL or CT2DATH & CT2DATL) when an event of CPTRU1 (or CPTRU2) is detected. One of three event (positive edge, negative edge, or any edge) can be selected by the CT1MD[1:0] bits (or CT2MD[1:0]) in the CT1CR (or CT2CR). To use this feature, the CPTRU1 pin (or CPTRU2 pin) should be assigned an input port by the port control register. Using the Capture Mode, external clock period or pulse width (high width or low width) can be measured.

Note: While in Capture mode, the CTDATH and CTDATL are still writable by S/W.

Figure 8.

Capture Timer in Capture Mode

## 9.5. Capture Timer Control Registers (CT1CR/CT2CR)

| Address   | D1H/E1H |   |   |   |   |   |   |   |

|-----------|---------|---|---|---|---|---|---|---|

| Bit Addr. |         |   |   |   |   |   |   |   |

| BIT       | 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| NAME                          | CT1EN<br>CT2EN    | CT1CNTL<br>R<br>CT2CNTL<br>R | CT1FS2<br>CT2FS2                                 | CT1FS1<br>CT2FS1                                 | CT1FS0<br>CT2FS0                                 | CT1MD1                                   | CT1MD1<br>CT2MD1                      | CT1MD0<br>CT2MD0                      |

|-------------------------------|-------------------|------------------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|------------------------------------------|---------------------------------------|---------------------------------------|

| Definition                    | C-Timer<br>ENable | C-Timer<br>counter<br>CLeaR  | C-Timer<br>input<br>Frequency<br>Select<br>bit-2 | C-Timer<br>input<br>Frequency<br>Select<br>bit-1 | C-Timer<br>input<br>Frequency<br>Select<br>bit-0 | C-Timer1<br>operation<br>MoDe<br>bit-2   | C-Timer<br>operation<br>MoDe<br>bit-1 | C-Timer<br>operation<br>MoDe<br>bit-0 |

| Reset<br>Value                | 0                 | 0                            | 0                                                | 0                                                | 0                                                | 0                                        | 0                                     | 0                                     |

| Read/<br>Write by<br>Software | R/W               | R/W<br>Always 0<br>read.     | R/W                                              | R/W                                              | R/W                                              | R/W for<br>C-Timer1<br>R for<br>C-Timer2 | R/W                                   | R/W                                   |

TABLE 10.

Definition of CT1CR/CT2CR

| Name                     | Bit    | Description (Note: n = 1 or 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CT1EN<br>CT2EN           | 7      | C-Timer ENable bit<br>[Bit Status: 0 (Initial Value)]<br>A selected input clock is halted. The CTnCNTH & CTnCNTL keeps counting<br>value.<br>[Bit Status: 1]<br>A selected input clock is run. The CTnCNTH & CTnCNTL counts up the negative<br>edge of the selected clock.                                                                                                                                                                                                                                              |

| CT1CNTLR<br>CT2CNTLR     | 6      | CTn counter CLeaR bit<br>If this bit is written with high, the CTnCNTH & CTnCNTL (16-bit up-counter) of<br>the C-Timer will be cleared to 0000H. Writing low will not affect anything. When<br>read, a low(0) will be always read.                                                                                                                                                                                                                                                                                      |

| CT1FS[5:3]<br>CT2FS[5:3] | 5 to 3 | C-Timer input clock Frequency Select bits<br>[Bit Status: 000 (Initial Value)] $F_{sys}/12$<br>[Bit Status: 001] $F_{fast}/2^4$<br>[Bit Status: 010] $F_{fast}/2^5$<br>[Bit Status: 011] $F_{fast}/2^7$<br>[Bit Status: 100] $F_{fast}/2^{10}$<br>[Bit Status: 101] $F_{fast}/2^{14}$<br>[Bit Status: 110] $F_{fast}/2^{18}$<br>[Bit Status: 111] CPTRU1 or CPTRU2<br>To use the CPTRU1 or CPTRU2 pin as an Event Input or Up Down-Count Input,<br>the pin should be assigned to input mode by a port control register. |

| CT1MD[2:0]<br>CT2MD[2:0] | 2 to 0 | C-Timer MoDe select bits<br>[Bit Status: 000 (Initial Value)]<br>Auto-Reload Mode<br>[Bit Status: 001]<br>Positive Edge Detect Capture Mode<br>[Bit Status: 010]<br>Negative Edge Detect Capture Mode<br>[Bit Status: 011]<br>Any Edge (Positive or Negative) Detect Capture Mode<br>[Bit Status: 1XX] (Capture-Timer1 only)<br>Up Down-Count Mode<br>CT2MD[2] of C-Timer2 is unused.                                                                                                                                   |

TABLE 11.

The Description of CT1CR/CT2CR

| Address                       | D6H                                                   |                      |                       |          |          |          |          |          |

|-------------------------------|-------------------------------------------------------|----------------------|-----------------------|----------|----------|----------|----------|----------|

| Bit Addr.                     |                                                       |                      |                       |          |          |          |          |          |

| BIT                           | 7                                                     | 6                    | 5                     | 4        | 3        | 2        | 1        | 0        |

| NAME                          | CT10VUN                                               | CT1OV                | CT1UN                 |          |          |          |          |          |

| Definition                    | C-Timer1<br>Overflow<br>and<br>Underflow<br>Interrupt | C-Timer1<br>Overflow | C-Timer1<br>Underflow | Reserved | Reserved | Reserved | Reserved | Reserved |

| Reset<br>Value                | 0                                                     | 0                    | 0                     | 0        | 0        | 0        | 0        | 0        |

| Read/<br>Write by<br>Software | R                                                     | R                    | R                     | R        | R        | R        | R        | R        |

## 9.6. Capture Timer-1 Status Registers (CT1SR)

TABLE 12.

Definition of CT1SR

| Name    | Bit    |                                                                                                                                                            |

|---------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CT1OVUN | 7      | C-Timer1 Overflow and Underflow Interrupt bit<br>[Bit Status: 0 (Initial Value)]: No Overflow and no Underflow.<br>[Bit Status: 1]: Overflow or Underflow. |

| CT1OV   | 6      | C-Timer1 Overflow bit<br>[Bit Status: 0 (Initial Value)]: No Overflow.<br>[Bit Status: 1]: Overflow.                                                       |

| CT1UN   | 5      | C-Timer1 Underflow bit<br>[Bit Status: 0 (Initial Value)]: No Underflow.<br>[Bit Status: 1]: Underflow.                                                    |

|         | 4 to 0 | Reserved bit                                                                                                                                               |

TABLE 13.

Description of CT1SR

| 9.7.  | C-Timer Counter Registers (CT1CNTH & CT1CNTL / |

|-------|------------------------------------------------|

| CT2CN | NTH& CT2CNTL)                                  |

| Address                       | D3H/E3H                                                                     |                                                                                                                                                                                                                                                                                                                                                 |                                                                             |                                                                             |                                                                             |                                                                             |                                                                             |                                                                             |  |

|-------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------|--|

| Bit Addr.                     | None                                                                        |                                                                                                                                                                                                                                                                                                                                                 |                                                                             |                                                                             |                                                                             |                                                                             |                                                                             |                                                                             |  |

| BIT                           | 7                                                                           | 6                                                                                                                                                                                                                                                                                                                                               | 5                                                                           | 4                                                                           | 3                                                                           | 2                                                                           | 1                                                                           | 0                                                                           |  |

| NAME                          | CTnCNTH[                                                                    | 7:0]                                                                                                                                                                                                                                                                                                                                            |                                                                             |                                                                             |                                                                             |                                                                             |                                                                             |                                                                             |  |

| Definition                    | (Auto-Reloa<br>CTnDATH &<br>(Capture M<br>(Up Down-0                        | C-Timer-n CouNTer register bit 15 to 8<br>Auto-Reload Mode: High 8-bit of the Modulo N Up-counter: 0000H to N-1, N is the content of<br>CTnDATH & CTnDATL)<br>Capture Mode: High 8-bit of the Modulo 65536 Up-counter: 00 to 65535)<br>Up Down-Count Mode: High 8-bit of the Modulo 65536 Up and Down- counter: 00 to 65535 (C-<br>ïmer1 only)) |                                                                             |                                                                             |                                                                             |                                                                             |                                                                             |                                                                             |  |

| Reset<br>Value                | 0                                                                           | 0                                                                                                                                                                                                                                                                                                                                               | 0                                                                           | 0                                                                           | 0                                                                           | 0                                                                           | 0                                                                           | 0                                                                           |  |

| Read/<br>Write by<br>Software | R                                                                           | R                                                                                                                                                                                                                                                                                                                                               | R                                                                           | R                                                                           | R                                                                           | R                                                                           | R                                                                           | R                                                                           |  |

| Write by<br>Hardware          | Written<br>with a new<br>count<br>value<br>0 or 1.<br>0 by<br>CTnCNTL<br>R. | Written<br>with a new<br>count<br>value<br>0 or 1.<br>0 by<br>CTnCNTL<br>R.                                                                                                                                                                                                                                                                     | Written<br>with a new<br>count<br>value<br>0 or 1.<br>0 by<br>CTnCNTL<br>R. | Written<br>with a new<br>count<br>value<br>0 or 1.<br>0 by<br>CTnCNTL<br>R. | Written<br>with a new<br>count<br>value<br>0 or 1.<br>0 by<br>CTnCNTL<br>R. | Written<br>with a new<br>count<br>value<br>0 or 1.<br>0 by<br>CTnCNTL<br>R. | Written<br>with a new<br>count<br>value<br>0 or 1.<br>0 by<br>CTnCNTL<br>R. | Written<br>with a new<br>count<br>value<br>0 or 1.<br>0 by<br>CTnCNTL<br>R. |  |

TABLE 14.

Definition of CTnCNTH (n = 1 or 2)

|            | [                                       |                                           |                |                                               |                    |             |   |   |

|------------|-----------------------------------------|-------------------------------------------|----------------|-----------------------------------------------|--------------------|-------------|---|---|

| Address    | D2H/E2H                                 |                                           |                |                                               |                    |             |   |   |

| Bit Addr.  | None                                    |                                           |                |                                               |                    |             |   |   |

| BIT        | 7                                       | 6                                         | 5              | 4                                             | 3                  | 2           | 1 | 0 |

| NAME       | CTnCNTL[7                               | <b>'</b> :0]                              |                |                                               |                    |             |   |   |

| Definition | (Auto-Reloa<br>CTnDATH &<br>(Capture Me | & CTnDATL)<br>ode: Low 8-b<br>Count Mode: | w 8-bit of the | 0<br>Modulo N U<br>dulo 65536 L<br>the Modulo | '<br>Ip-counter: 0 | 0 to 65535) |   |   |

| Reset<br>Value                | 0                                                                           | 0                                                                           | 0                                                                           | 0                                                                           | 0                                                                           | 0                                                                           | 0                                                                           | 0                                                                           |

|-------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| Read/<br>Write by<br>Software | R                                                                           | R                                                                           | R                                                                           | R                                                                           | R                                                                           | R                                                                           | R                                                                           | R                                                                           |

| Write by<br>Hardware          | Written<br>with a new<br>count<br>value<br>0 or 1.<br>0 by<br>CTnCNTL<br>R. |

TABLE 15.

Definition of CTnCNTL (n = 1 or 2)

| Name                           | Bit     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CTnCNTH[7:0] &<br>CTnCNTL[7:0] | 15 to 0 | C-Timer-n CouNTer bits<br>[Auto-Reload Mode]<br>A Modulo-N (0000H to N-1) up-counter. N is the content of CTnDATH &<br>CTnDATL. This counter counts up from 0000H to N-1. Then, the counter will go<br>back to 0000H and the comparator will generate match signal. The Match signal<br>will issue an interrupt request. The counter will not stop after the Match. Thus,<br>any C-Timer will generate continuous Match signals with a fixed period.<br>[Capture Mode]<br>A Modulo-65536 (0000H to 65535) up-counter. This counter counts up from<br>0000H to 65535. Then, the counter will go back to 0000H and the CTnINT will be<br>set to high. The counter will not stop after the overflow. Thus, any C-Timer over-<br>flow will generate continuous interrupt request with a fixed period.<br>[Up Down-Count Mode] (Capture-Timer1 only)<br>A Modulo-65536 (0000H to 65535) up and down-counter. This counter counts<br>up on the negative edge of CPTRU1 and counts down on the negative edge of<br>CPTRD1. Either the overflow or the underflow will set CTnINT bit. The counter<br>will not stop after the overflow. Thus, any C-Timer1 overflow<br>and underflow will generate continuous interrupt request. |

TABLE 16.

The Description of CTnCNTH & CTnCNTL

# 9.8. C-Timer Data Register (CT1DATH & CT1DATL / CT2DATH & CT2DATL)

Address D5H/E5H

| Bit Addr.                     | None                                                                                                                  |               |                                                                                                                       |                                                                                                                       |                                                                                                                       |                                                                                                                       |                                                                                                                       |                                                                                                                       |  |  |  |  |  |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| BIT                           | 7                                                                                                                     | 6             | 5                                                                                                                     | 4                                                                                                                     | 3                                                                                                                     | 2                                                                                                                     | 1                                                                                                                     | 0                                                                                                                     |  |  |  |  |  |

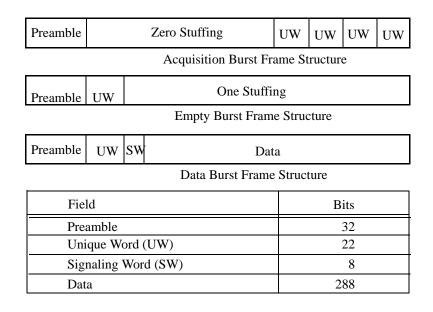

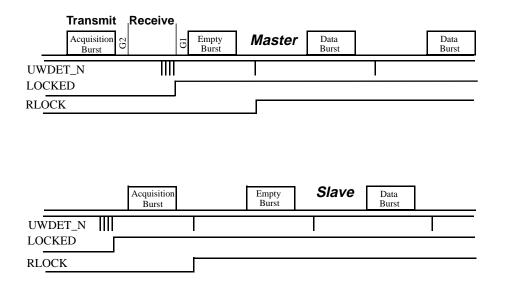

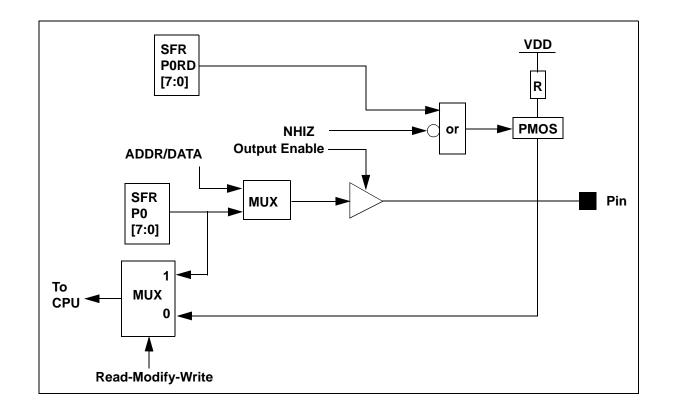

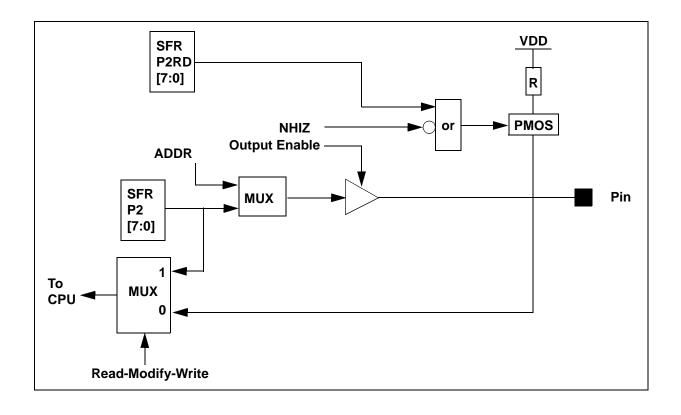

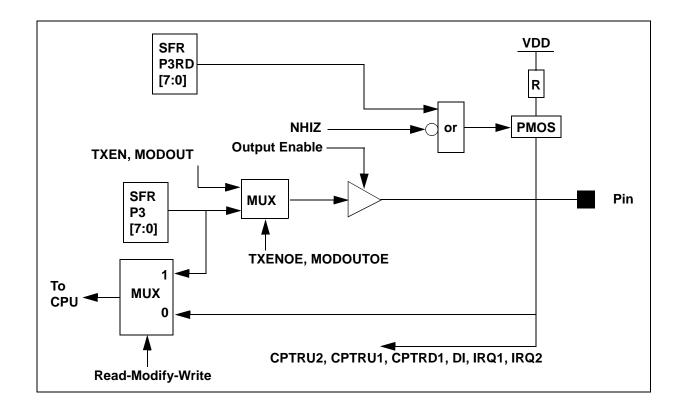

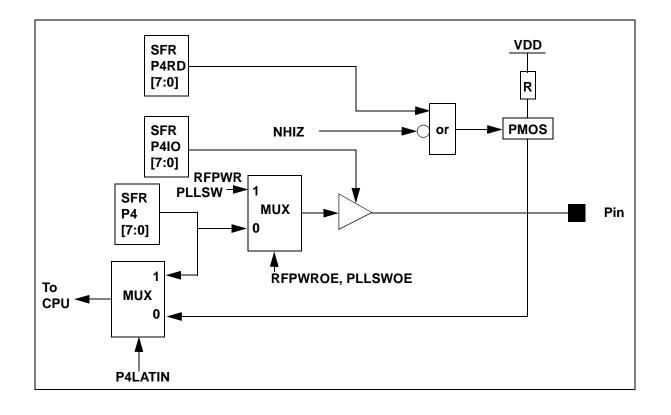

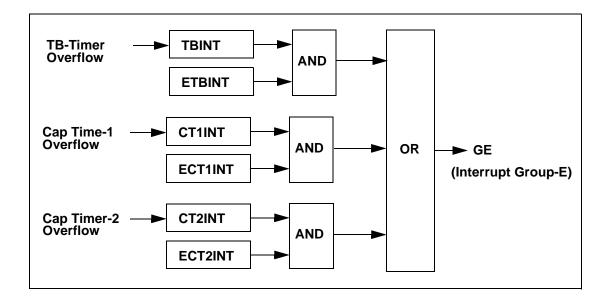

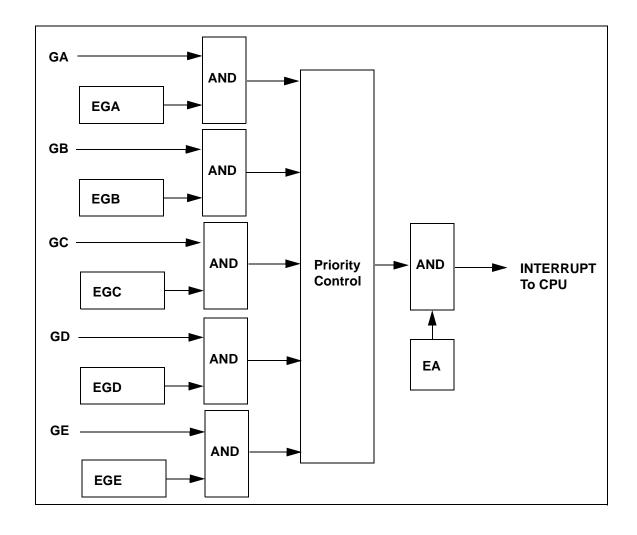

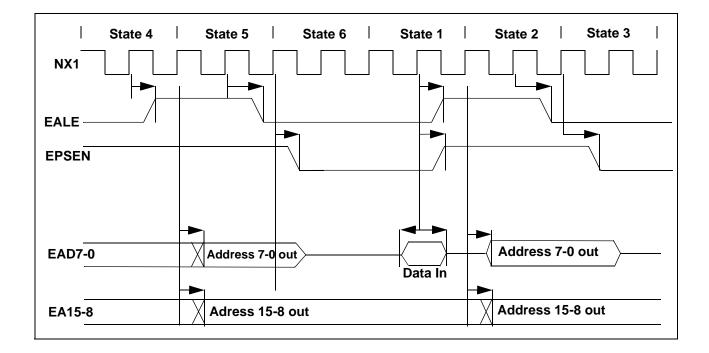

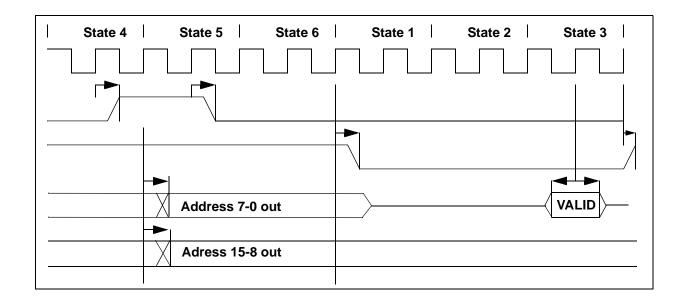

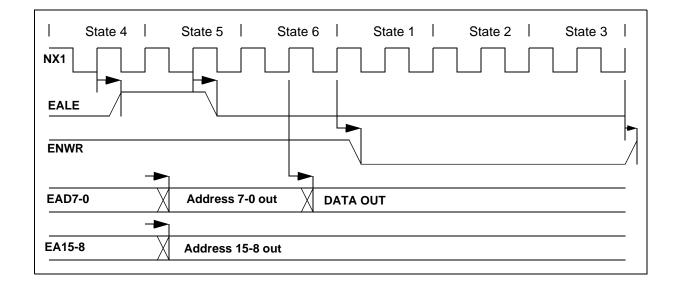

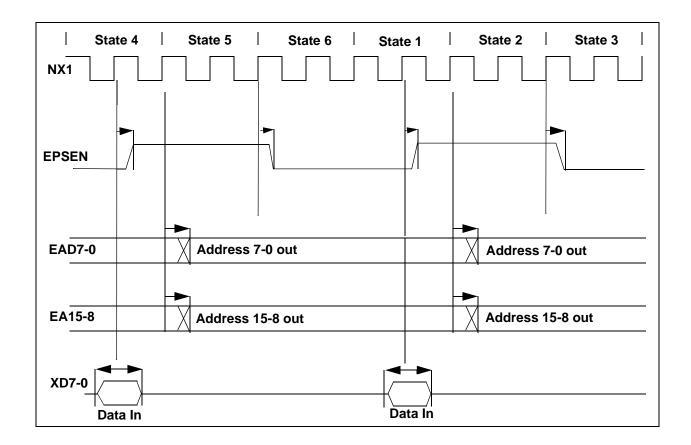

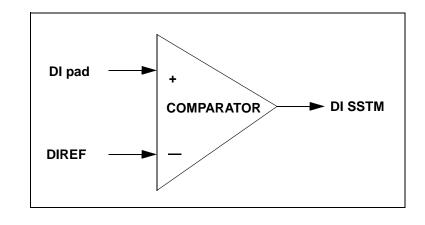

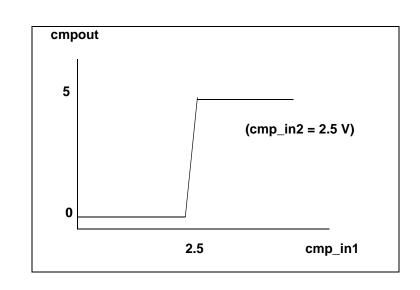

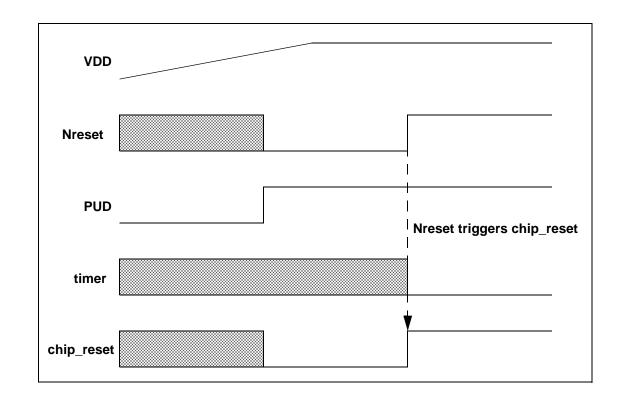

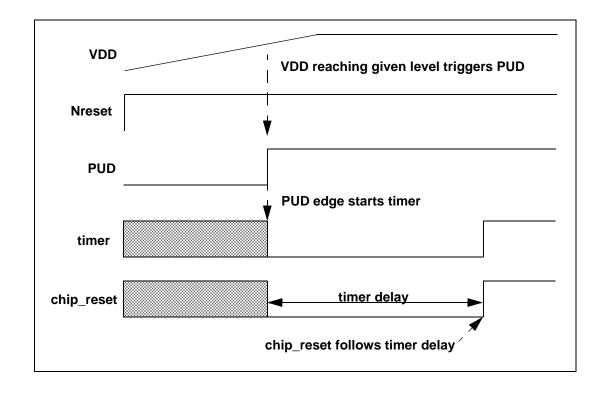

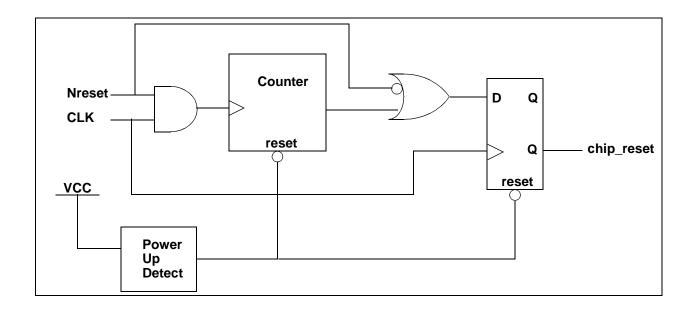

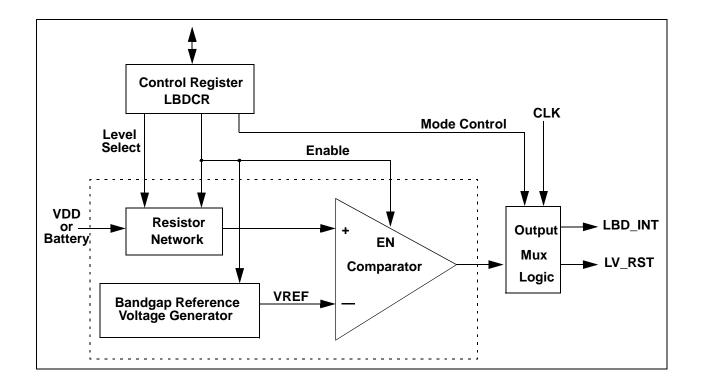

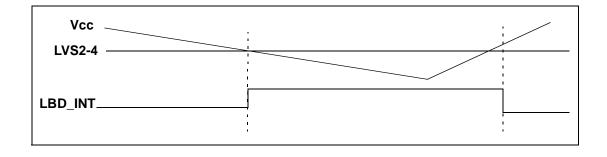

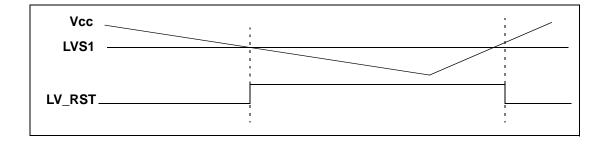

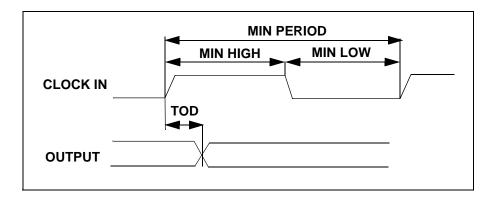

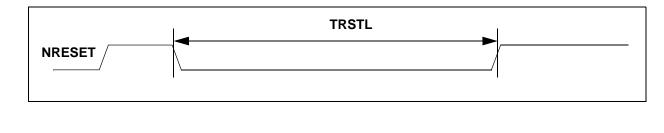

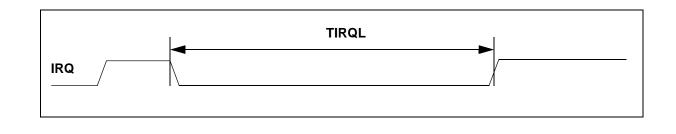

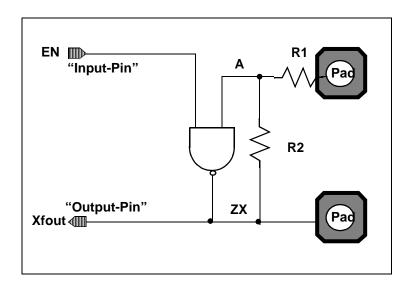

| NAME                          | CTnDATH[7                                                                                                             | CTnDATH[7:0]  |                                                                                                                       |                                                                                                                       |                                                                                                                       |                                                                                                                       |                                                                                                                       |                                                                                                                       |  |  |  |  |  |